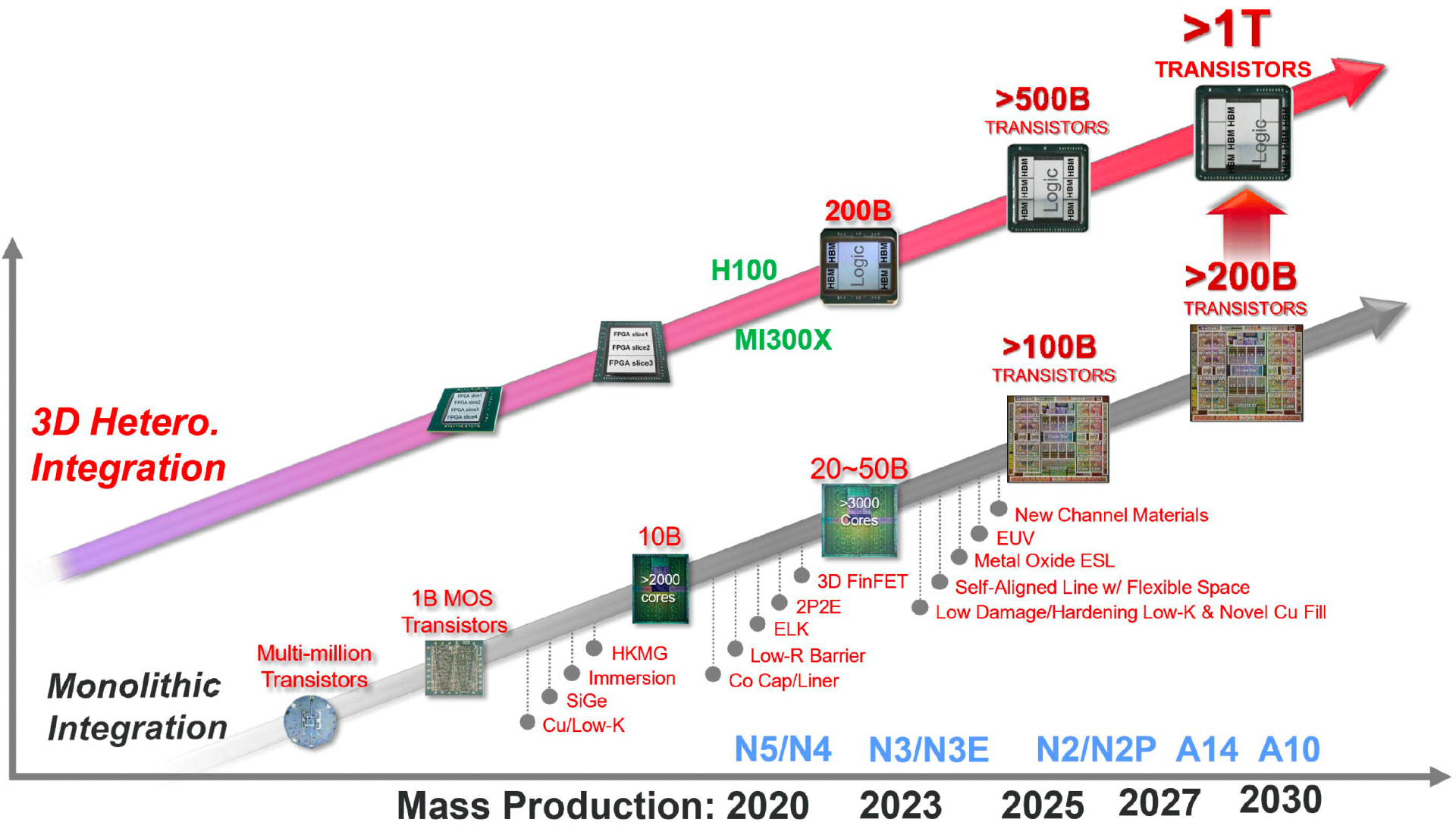

TSMC окреслила плани помістити понад 1 трлн транзисторів у 3D-пакуванні та 200 млрд у монолітних чіпах до 2030 року. Під час конференції IEDM 2023 компанія показала дорожню карту щодо того, яким має бути її напівпровідниковий «портфель», і, схоже, тайванський гігант має амбітні плани на кінець цього десятиліття.

Виходячи з оприлюдненої дорожньої карти, TSMC впевнена, що її техпроцеси знаходяться на правильному шляху: дебют техпроцесів TSMC N2 і N2P відбудеться у 2025-2027 роках, а передові техпроцеси A10 (1 нм) і A14 (1,4 нм) заплановані на 2027-2030 роки. Окрім зменшення технологічних процесів, TSMC планує досягти значних успіхів і в інших напівпровідникових технологіях, встановивши орієнтири для галузі, повідомляє Wccftech.

Цікавіше те, що тайванський гігант розкрив досягнення у двох ключових секторах напівпровідникової індустрії — монолітних конструкціях та 3D гетероінтеграції (або чиплетних конструкціях). Промисловість дійсно зміщується в бік чиплетних конфігурацій, оскільки вони пропонують модульність та економічні переваги.

AMD використовує дизайн мікросхем TSMC для своїх новітніх споживчих чипів, мікросхем для центрів обробки даних, а тепер і для новітніх чипів прискорювачів MI300. Intel також випустила свої Meteor Lake, які є першою розробкою синьої команди для споживчих платформ, натякаючи на те, що майбутнє за чиплетами, і TSMC на крок попереду. Сама Intel для Meteor Lake користується технологічними процесами TSMC. Компанія прогнозує, що до 2030 року 3D-гетероінтеграція досягне колосального обсягу в «один трлн транзисторів».